ICP刻蚀4H-SiC栅槽工艺研究

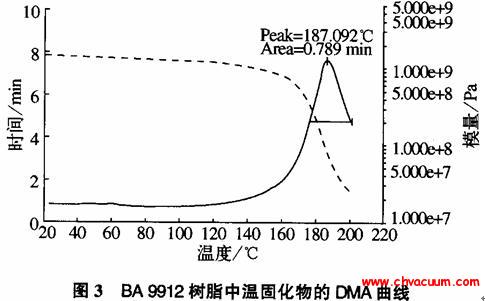

为避免金属掩膜易引起的微掩膜,本文采用SiO2介质作为掩膜,SF6/O2/Ar作为刻蚀气体,利用感应耦合等离子体刻蚀(ICP)技术对4H-SiC trench MOSFET栅槽刻蚀工艺进行了研究。本文详细研究了ICP刻蚀的不同工艺数对刻蚀速率、刻蚀选择比以及刻蚀形貌的影响。实验结果表明:SiC刻蚀速率随着ICP功率和RF偏压功率的增大而增加;随着气体压强的增大刻蚀选择比降低;而随着氧气含量的提高,不仅刻蚀选择比增大,而且能够有效地消除微沟槽效应。刻蚀栅槽形貌和表面粗糙度分别通过扫描电子显微镜和原子力显微镜进行表征,获得了优化的栅槽结构,RMS表面粗糙度<0.4nm。

由于SiC具有宽禁带(2.3~3.3eV)、高临界击穿电场(3×106 V/cm)、高饱和电子漂移速度(2×107 cm/s)、高热导率(4.9 W/(cm· K))等优点,使得SiC材料在制备大功率、高温、高频、抗辐射的半导体器件等方面具有极其广泛的应用。

然而,SiC材料硬度高、化学性质稳定,难以通过湿法腐蚀形成各种结构,目前只能采用干法刻蚀的方法。对于SiC槽栅结构器件如UMOSFET、Trench Gate IGBT以及SiC MEMS器件等三维结构器件,刻蚀形貌、刻蚀损伤以及刻蚀表面残留物等均对SiC器件的研制及性能有很大的影响。目前刻蚀SiC最常用的气体是F基气体,如CF4、SF6,本次实验采用了SF6/O2/Ar作为刻蚀气体。由于采用金属做掩膜,容易在刻蚀过程中金属簇会溅射到SiC表面,而金属刻蚀速率远小于SiC刻蚀速率,从而导致微掩的形成,为了消除微掩膜效应以及残留金属的污染,本实验采用了高陡直的SiO2介质作为刻蚀掩膜,通过扫描电镜(SEM)观测和原子力显微镜(AFM)观测发现刻蚀表面很光滑,实验中RMS表面粗糙度为0.36nm,未出现微掩膜;通过调节刻蚀参数,可以实现高刻蚀选择比的SiC刻蚀。

在SiC的刻蚀工艺中,如何消除“微沟槽”是该工艺中的难点,微沟槽指在临近侧壁的底部形成的V形凹槽,它主要是由于该处刻蚀速率增强造成的;微沟槽的存在会导致器件的电场集中,降低器件的稳定性和可靠性,本文对微沟槽消除方法进行了探究,最终获得了高刻蚀速率、高陡直性、高刻蚀选择比、无微沟槽且底脚圆滑的栅槽刻蚀工艺条件。

1、实验步骤

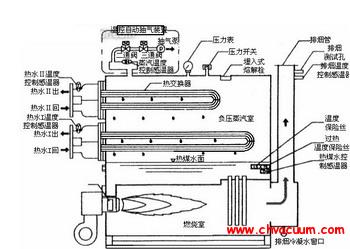

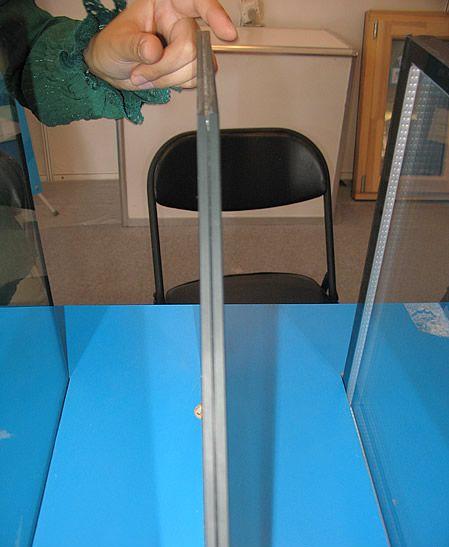

本实验采用4H-SiC衬底作为刻蚀材料,经常规清洗后,等离子增强化学气相沉积(PECVD)生长2μm厚SiO2作为SiC刻蚀的硬掩膜,之后LPCVD生长100nm非晶硅,此非晶硅作为刻蚀SiO2的掩膜,刻蚀图形为宽度3μm 长条形区域。对非晶硅和SiO2的刻蚀分别利用Lam Research 公司的Rainbow 4420和Rainbow 4520,对SiC的刻蚀采用德国Sentech公司的SI500系列ICP刻蚀机。为了研究不同刻蚀参数对SiC刻蚀速率、刻蚀选择比、微沟槽的消除的影响,选用了如下的刻蚀条件:ICP功率变化范围为400~800 W,偏压功率为30~200W,刻蚀压强为0.2~2Pa,通过改变O2的流速使得O2含量变化范围为10%~50%来研究氧气含量对刻蚀效果的影响。通过SEMS-5500观测刻蚀形貌和刻蚀深度,利用AFM 分析了样品刻蚀的表面粗糙度的变化情况。

3、结论

为避免金属掩膜易引起的微掩膜,本文采用SiO2作为掩膜,详细研究了不同工艺参数包括ICP功率、RF偏压功率、压强、氧气含量等对SiC槽栅区域的刻蚀速率、SiC与SiO2的刻蚀选择比、刻蚀形貌的影响。研究结果表明可通过调节ICP功率和RF功率优化SiC刻蚀速率,可通过调节压强和O2含量调节刻蚀选择比,重点研究了消除微沟槽的方法。最终获得了高刻蚀速率,高陡直性,高刻蚀选择比,无微沟槽且底脚圆滑的优化刻蚀工艺条件。在ICP功率为800 W,RF功率为100 W,反应室压强为0.4Pa,SF6/O2/Ar流量为15/45/30的刻蚀条件下,刻蚀陡直性好,底部平整,无微沟槽且底脚圆滑的刻蚀效果,刻蚀速率约500nm/min。本文对高质量SiC栅槽工艺及各种栅槽结构SiC器件的研发具有一定借鉴意义。